The Imposter is Suss (MicroTec)

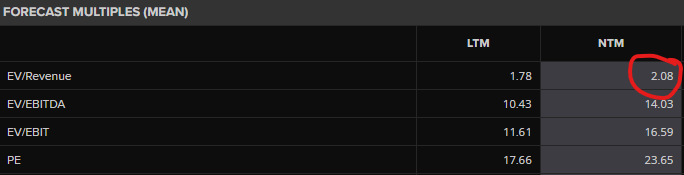

Suss MicroTec has near 100% revenue exposure to leading edge semiconductor equipment (advanced packaging & front-end logic) trading at EV/Revenue multiples 1/3 to 1/5 of US semicap majors.

Investing is like Among Us.

Our job is to look for imposters. In our universe of equities, which don’t belong? Which are mispriced? By looking for the outliers, we generate alpha.

Today, the imposter is Suss. (pun intended)

Contents

Introduction

Advanced Packaging

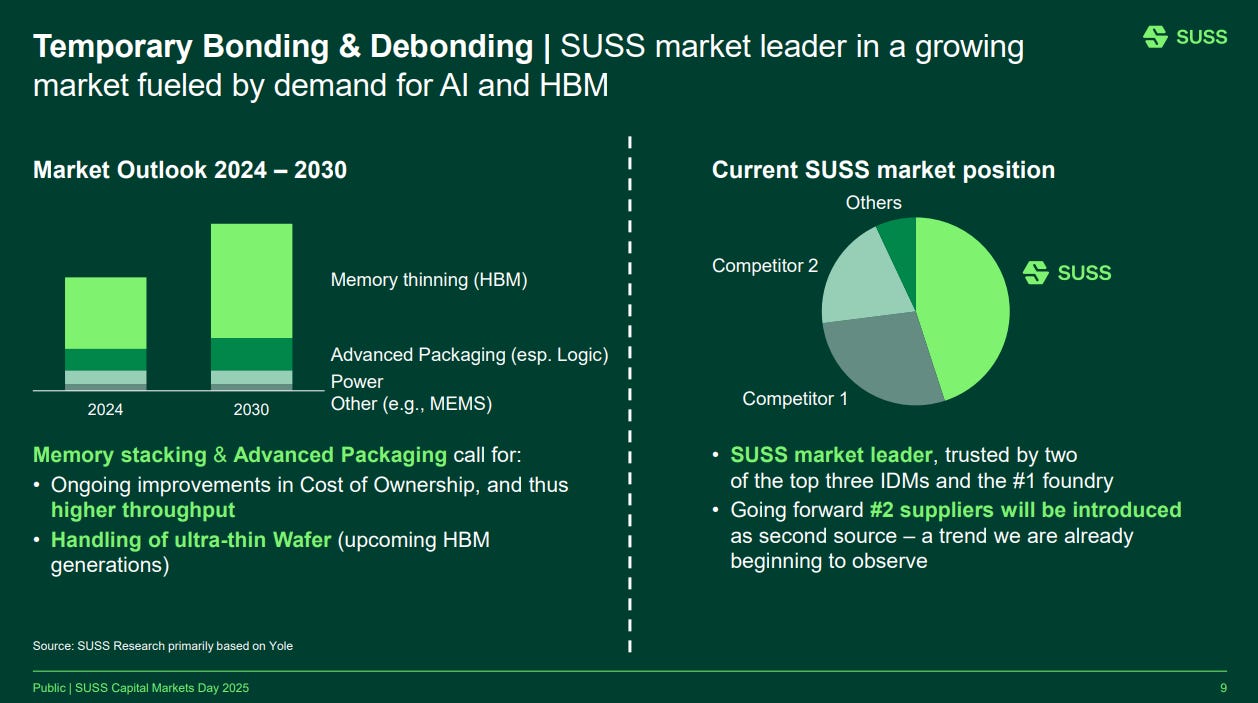

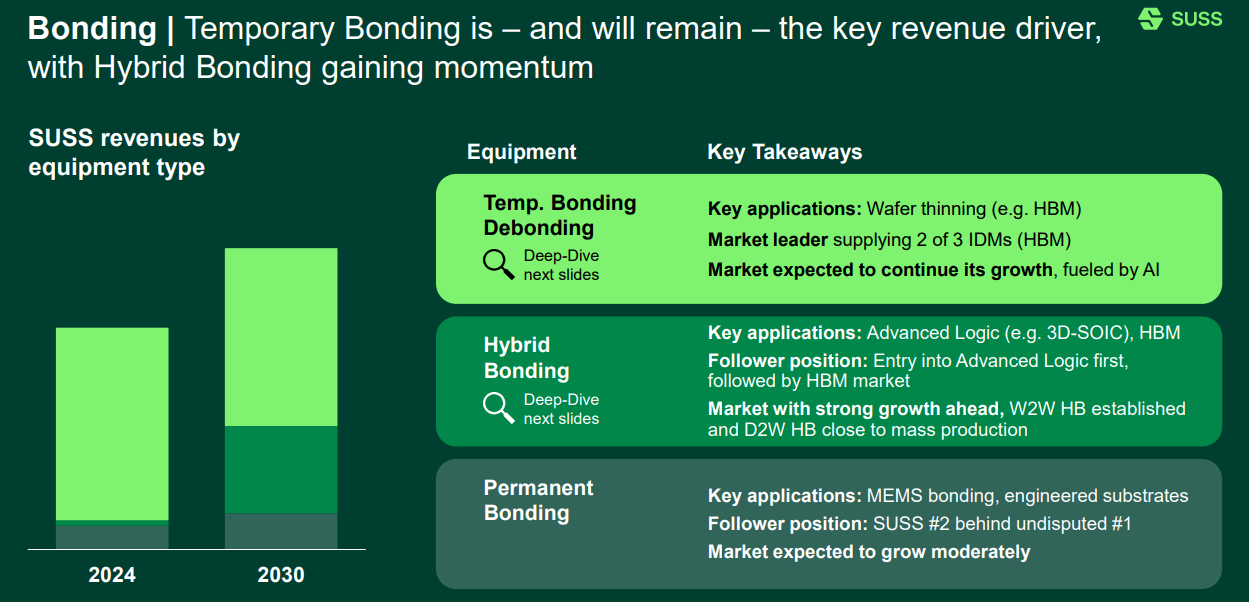

Temporary Bonding

Hybrid Bonding

Coaters & Developers

Mask Aligners & UV Scanners

Front-End Photomask Solutions

Cyclical Trough

Revenue Build, EPS Estimates, DCF Model

By accessing this content, you acknowledge and agree to our terms and conditions. This research is not financial advice.

I can build you custom models for any semis/AI company. If interested, please reach out at jasonschips@gmail.com.

Introduction

The thesis is both really simple and really complicated. Really simple because you can describe it in one sentence:

Suss MicroTec has near 100% revenue exposure to leading edge semiconductor equipment (advanced packaging & front-end logic) trading at EV/Revenue multiples 1/3 to 1/5 of US semicap majors.

Really complicated because they have 6 distinct product segments that each have their own market dynamics.

So where should we start?

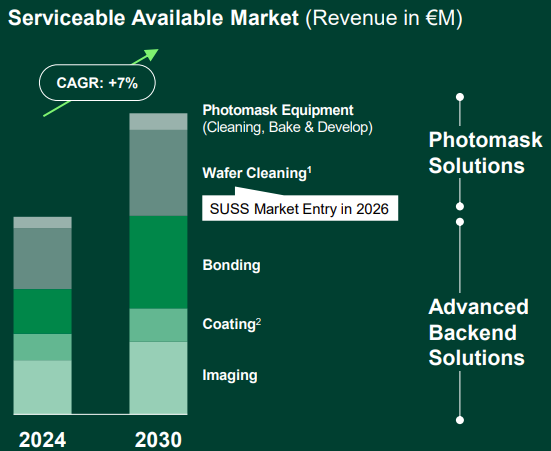

Suss MicroTec gets 70% of their revenue from advanced packaging and 30% from the front-end.

In advanced packaging, they sell five types of tools: Temporary Bonders, Hybrid Bonders, Coaters & Developers, UV Scanners, and Mask Aligners.

They participate in the front-end through Photomask Solutions, which include cleaning tools and bake & develop tools.

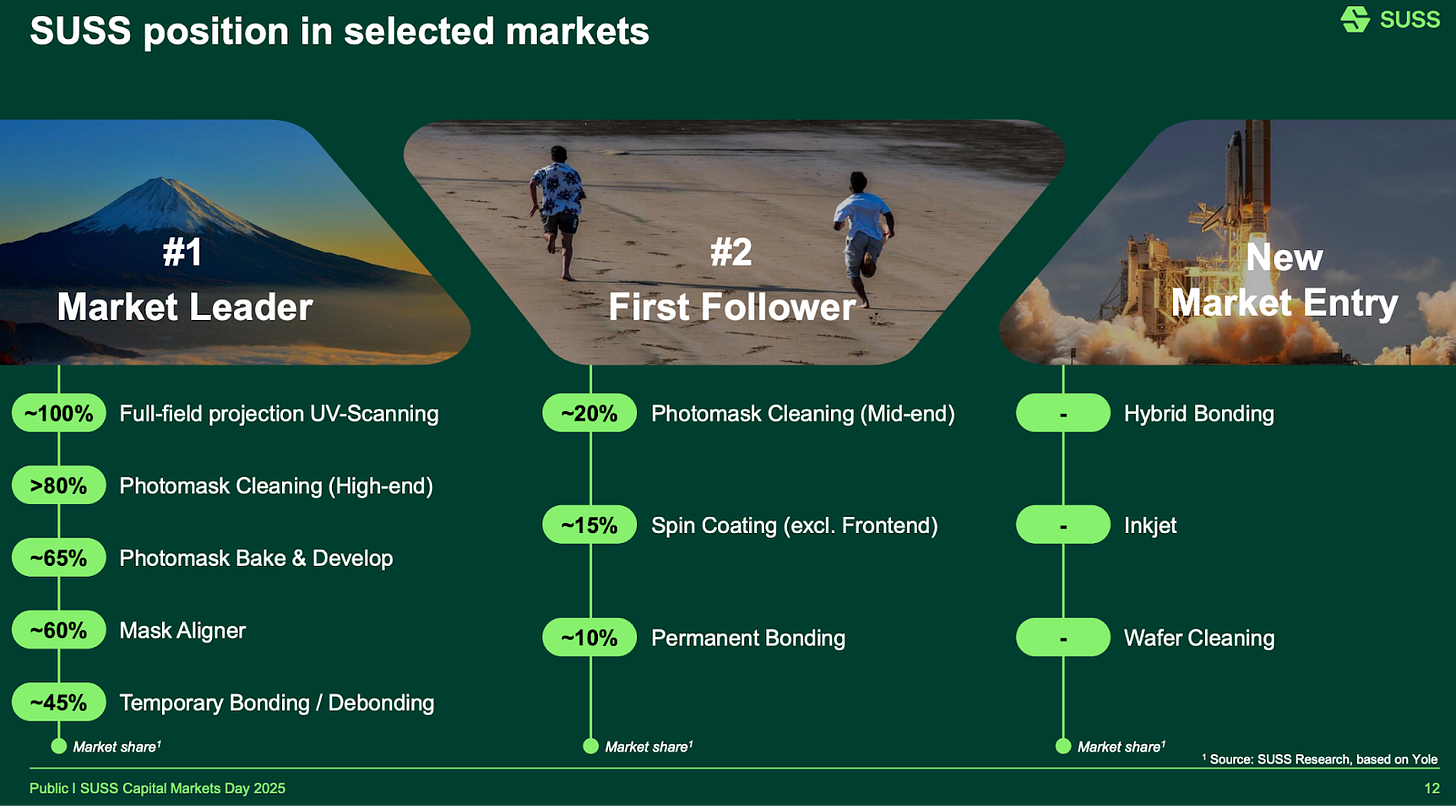

A couple of their tools are monopolies, a couple have majority market share, and a bunch of them are new entrant call options.

And this is all inside a little company worth less than €1b.

Since there are so many damn tools and markets and cool stuff that they do this writeup unfortunately has to remain quite surface level.

Advanced Packaging

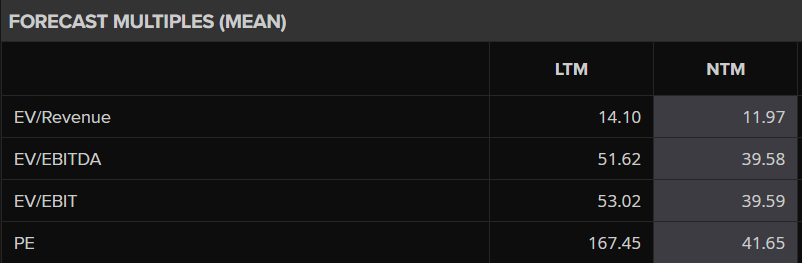

Advanced packaging semicap names are a fan favorite. See Camtek multiples:

This is because advanced packaging gives you pure exposure to AI-related fab capex. Which is actually a lot harder than you think if you really try to dig around for semicaps. AMAT and friends very diversified. Front-end names are great but you really have two choices there: ASML and KLA. Both of which I like a lot but are very expensive.

There is a caveat that leading edge logic is probably a more attractive market than advanced packaging nowadays since “CoWoS bottleneck” is very 2024 coded and we’ve moved on to N3 capacity bottleneck. But that doesn’t mean you can’t get great returns in advanced packaging.

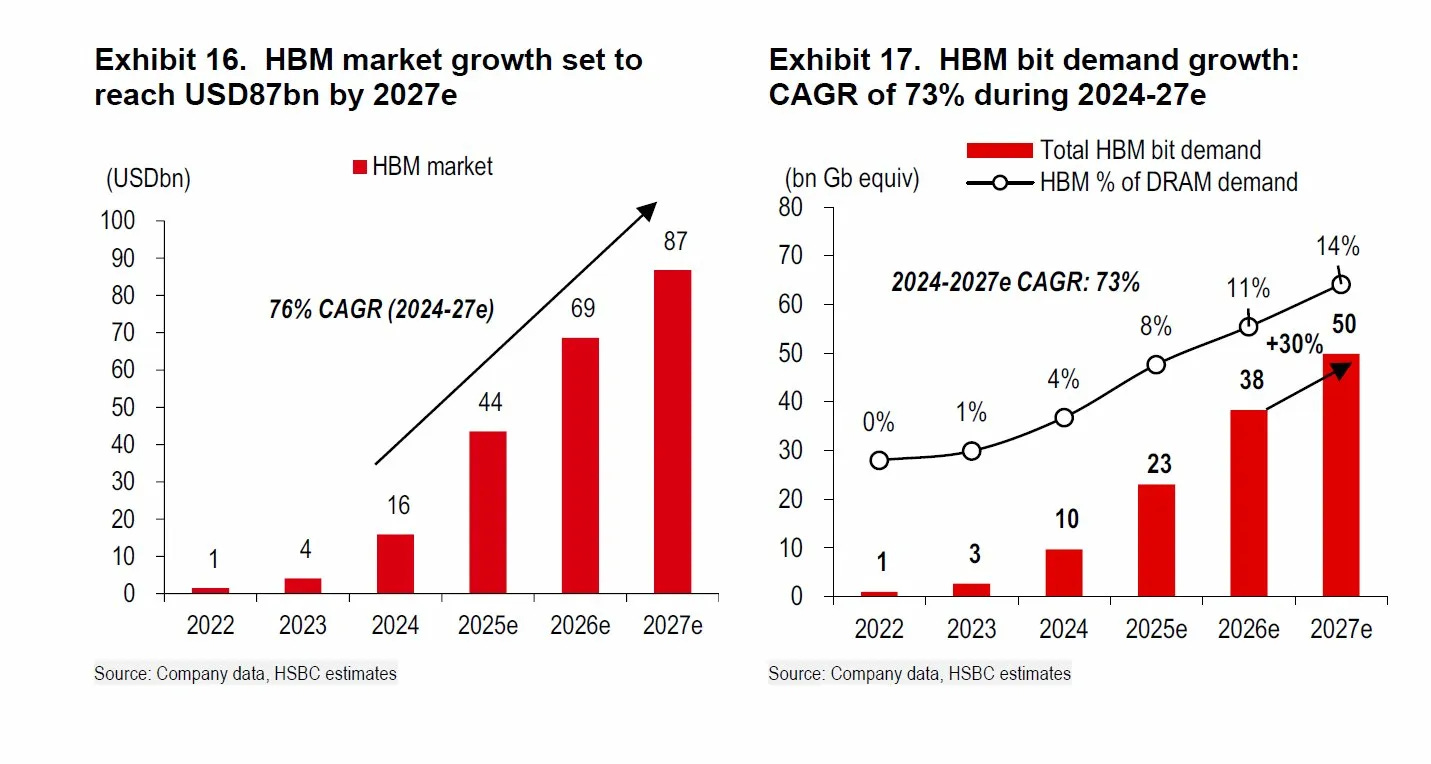

You do not have to be a wizard to figure out that this is a good market. There are basically two end markets: CoWoS and HBM. Both scale-ish with Nvidia shipments and should outgrow overall WFE.

Temporary Bonding

HBM is a stack of pancakes.

Where each of the DRAM die “pancakes” within the HBM stack is actually a lot thinner than a regular DRAM die.

So thin that you literally can’t transport them around the fab because it would be like trying to pick up wet tissue paper.

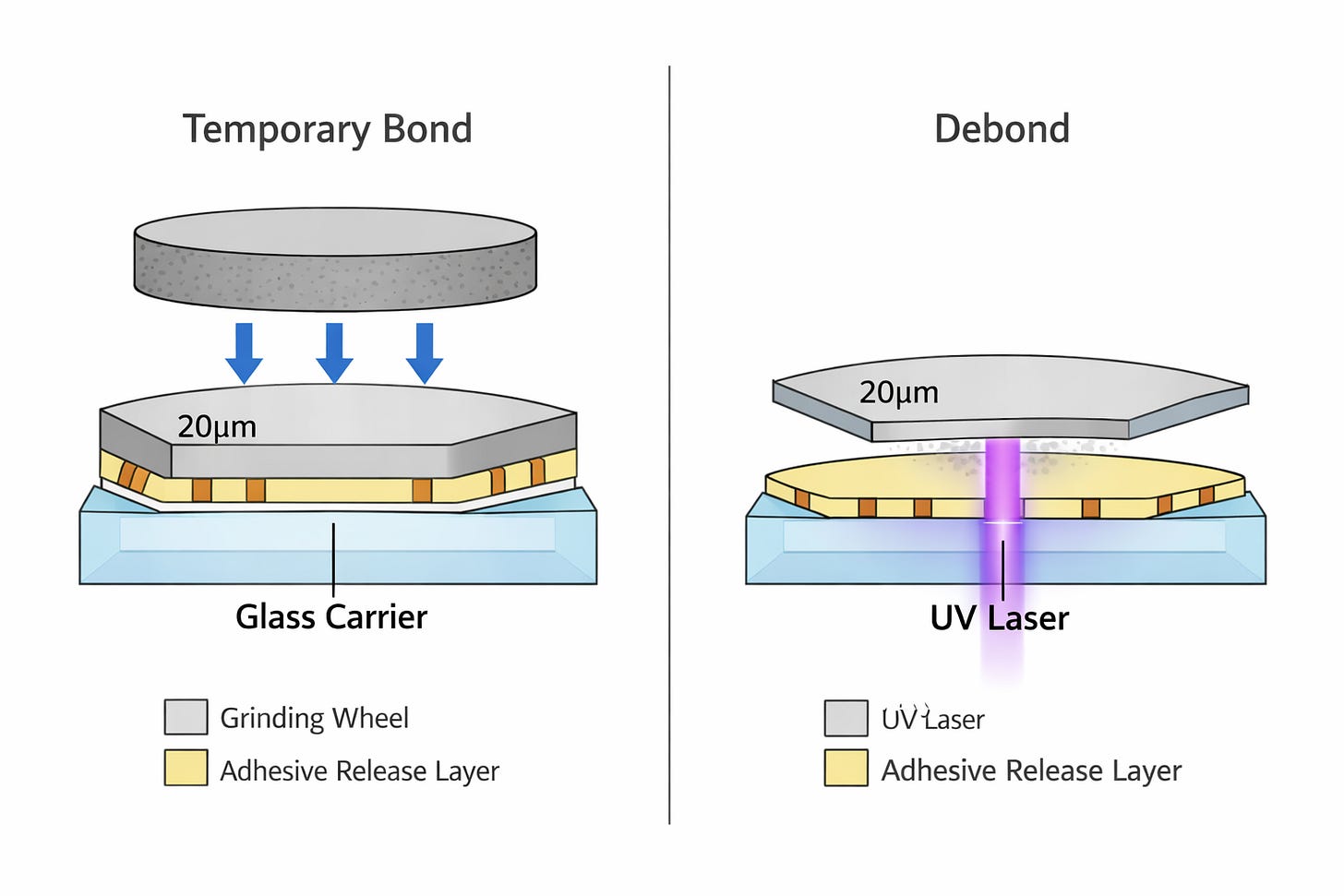

But as with all things in semiconductors, the impossible is always possible. Suss has a solution.

Temporarily bond the wet-tissue active wafer to a hard rigid glass carrier. This carrier provides mechanical support throughout all various fab processes like grinding, TSV formation, and interconnect steps. Once processing is complete, the bond is released (via UV laser) and the wafer is transferred for stacking.

Suss has 45% share overall but at TSMC they actually have 90%+ share.

In the rest of the market, they have 70% share at Samsung and Micron but no share at SK Hynix.

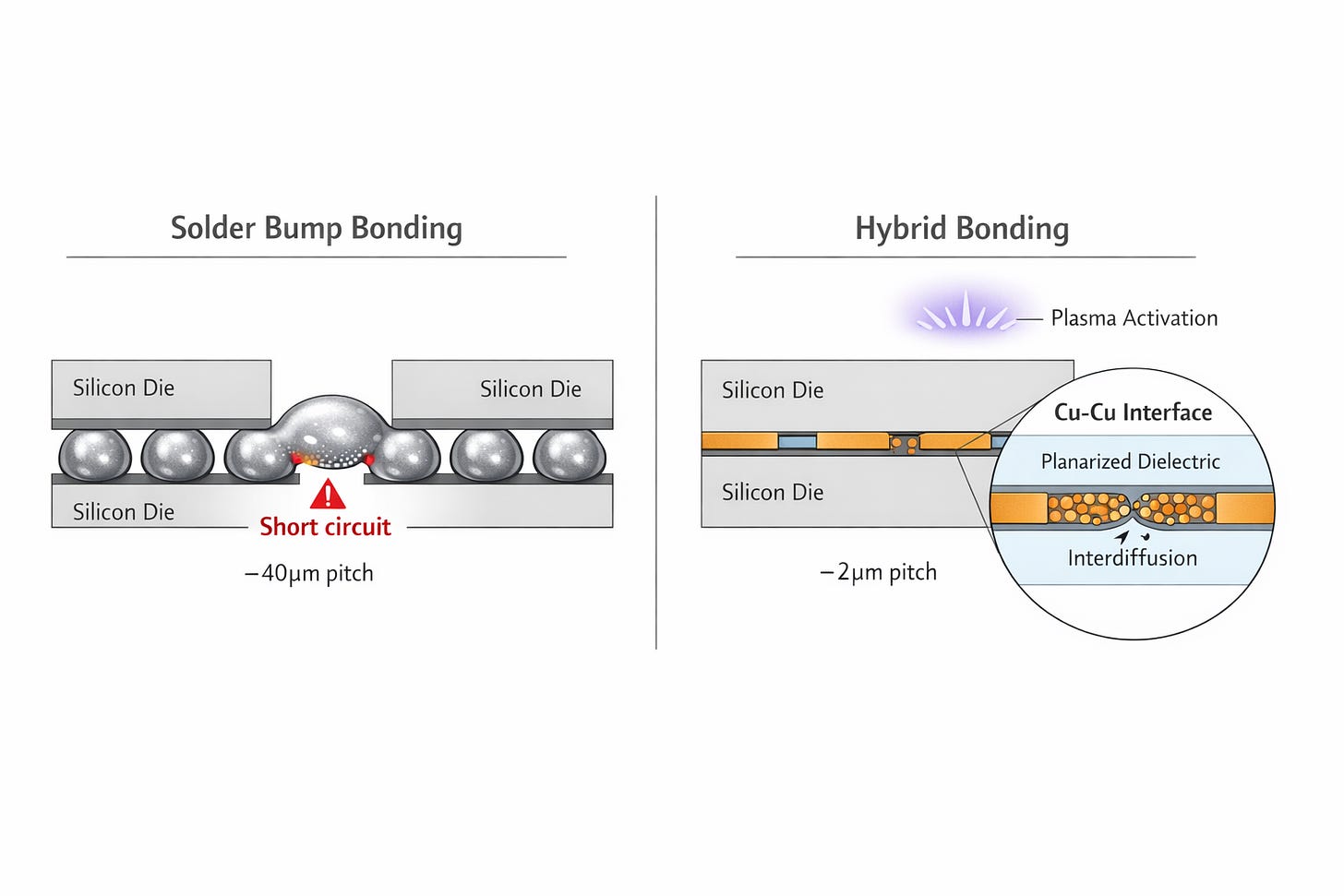

Hybrid Bonding

For the uninitiated, hybrid bonding is pressing two chips together, so the copper pads align and fuse with each other.

If you’ve never researched packaging, that sounds like common sense.

But the traditional way is actually using solder balls. Big spherical things that prevent you from packing connections tightly (or else you get short circuit). See why everyone is so excited about hybrid bonding?

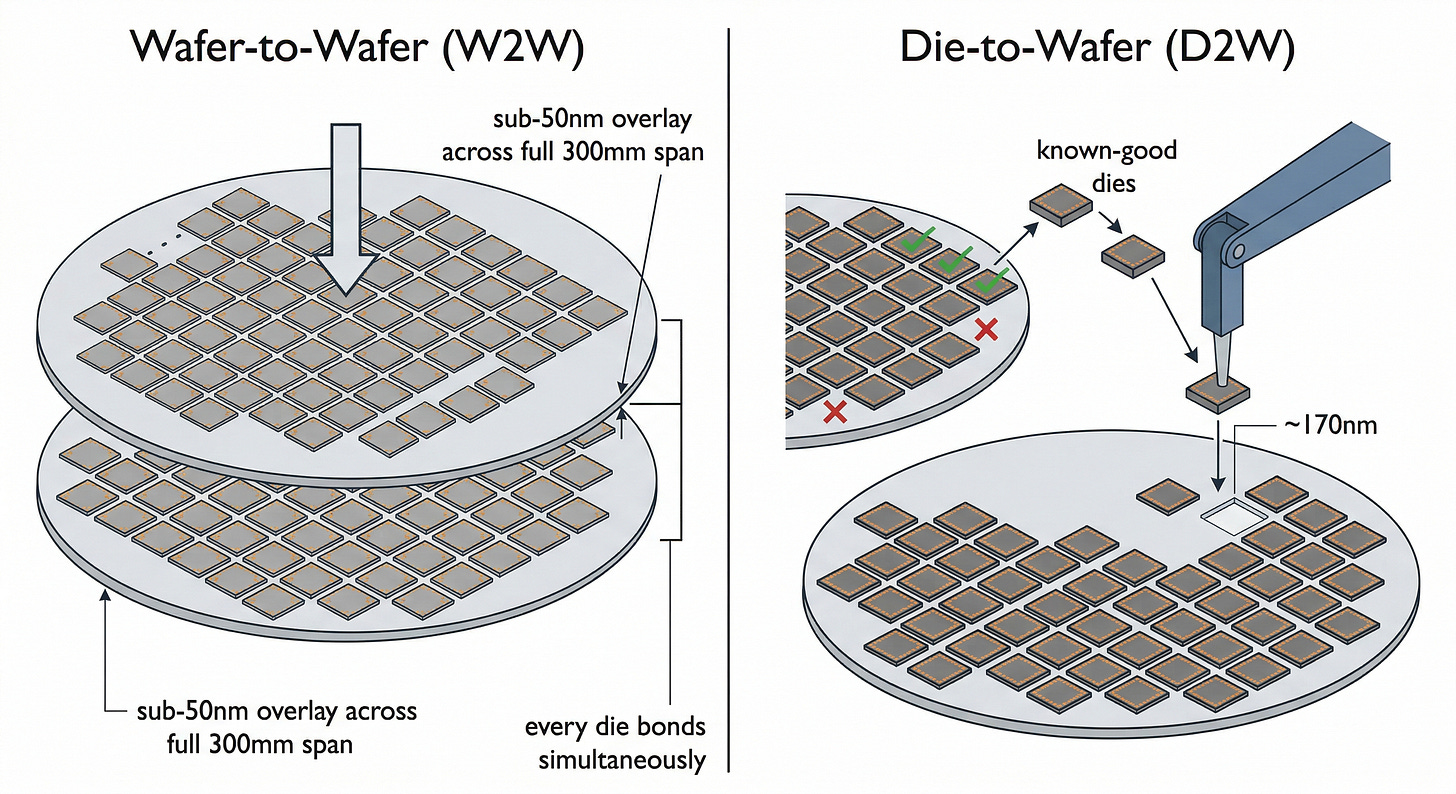

There are two main types of hybrid bonding.

Wafer-to-wafer and die-to-wafer. Hopefully I don’t need to explain to you what these mean.

Wafer-to-wafer has bad yield and good throughput. You don’t know if the dies you’re bonding are good, but you can bond lots of them. Die-to-wafer has good yields but is sloooow.

But good yields are very important so D2W is much more commonly used.

Suss is not the leader here. But if you think you can pick up a hybrid bonding leader at €1b… lol.

(Besi is 14x the size of Suss.)

But if they can break into the market it would be huge. Management thinks they can get a slice, enough for it to be 1/2 as big as their temporary bonding franchise by 2030. The cool thing about being a smol company is that even a small slice makes a big difference.

Their focus is mostly W2W. As you can see only one of those tools above is for D2W specifically.

What’s their wedge?

First, they are really good at surface prep because that skill carries over from temporary bonding. If the surface prep isn’t perfect, the bond fails regardless of alignment accuracy, so in fact customers may want the prep and bond steps from a single qualified vendor.

Second, any dual sourcing is a tailwind. Foundries like dual sourcing to reduce vendor risk. Pretty simple.

Third and most importantly, they have a proprietary hybrid boning technology called the hybrid bonding pin.

The core technical challenge in W2W hybrid bonding is air entrapment. Bring two wafers together flat and air gets trapped between them, preventing the van der Waals bond from forming and delaminating under thermal anneal. This pin imperceptibly bows the top wafer into a controlled convex shape, initiating contact at the geometric center and letting the bond wave propagate outward radially, pushing air ahead of it rather than trapping it. By precisely controlling the pin’s retraction speed, SUSS manages the mechanical wave propagation to minimize shear stress as the two crystal lattices lock together.

The result is sub-50nm post-bond overlay accuracy. Which is an important performance metric. Which positions SUSS as the credible second source.

Coaters & Developers

If you watched one of the dozens of YouTube videos about ASML you know what spin coating is.

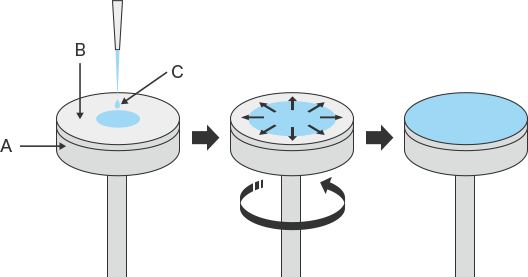

Before lithography you need to coat the wafer with photoresist. To do that you dispense it over the center and then spinnnnnn.

This process is needed in the backend too. Why? Because lithography is also needed in the backend to pattern the redistribution layers that are basically the roads that connect the chips on the CoWoS wafer or whatever your favorite packaging platform is.

Suss has a fairly small 15% share here and are #3. #1 is TEL.

As such, margins are pretty bad for spin coaters. Simple product and fragmented market.

But spin coaters have problem.

If you spin the wafer your stuff unfortunately gets flung off the surface. In fact, roughly 95% of the photoresist you dispensed ends up as waste. Backend photoresist is very expensive.

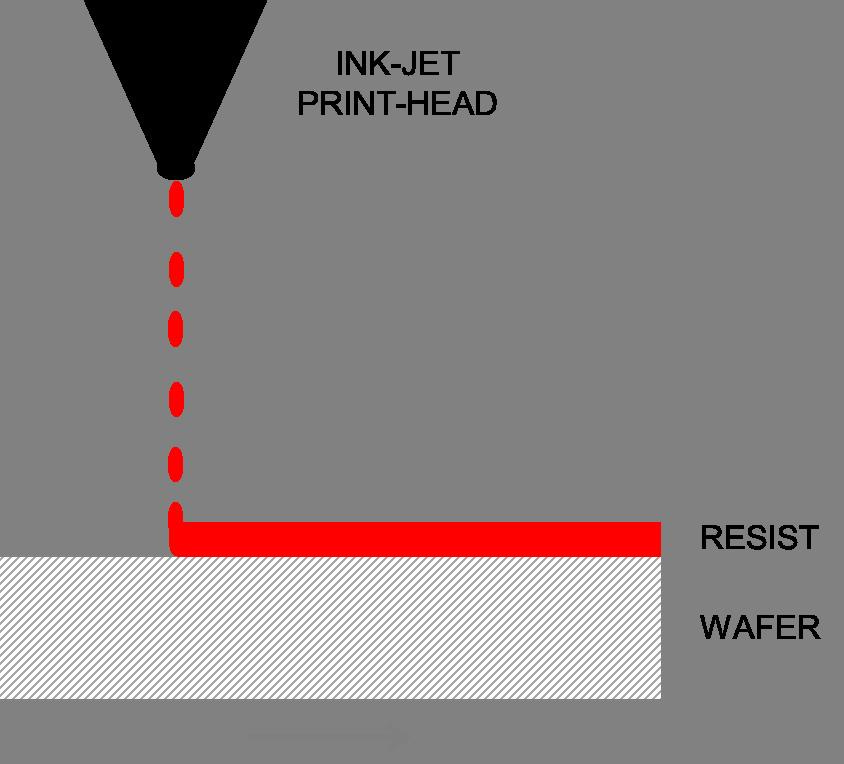

So there is a new type of tool in the market called Inkjet.

Instead of flooding the surface and letting centrifugal force do the work, you precisely jet droplets exactly where you need them. Utilization goes from ~5% to close to 100%.

Why did SUSS enter inkjet?

Mostly innovator’s dilemma. Spin coating gets progressively less viable over time. In addition, there are a bunch of incentives for Suss to be early.

Inkjet has meaningfully higher margins than spin coating because the process complexity creates a pricing umbrella that TEL can’t as easily erode. And the chemical savings give customers a compelling ROI story that makes the tool easier to sell even at a premium.

Mask Aligners & UV Scanners

These two tools do two different versions of the same thing.

In the coaters section I said

…lithography is also needed in the backend to pattern the redistribution layers that are basically the roads that connect the chips on the CoWoS wafer or whatever your favorite packaging platform is.

These tools are responsible for that actual lithography.

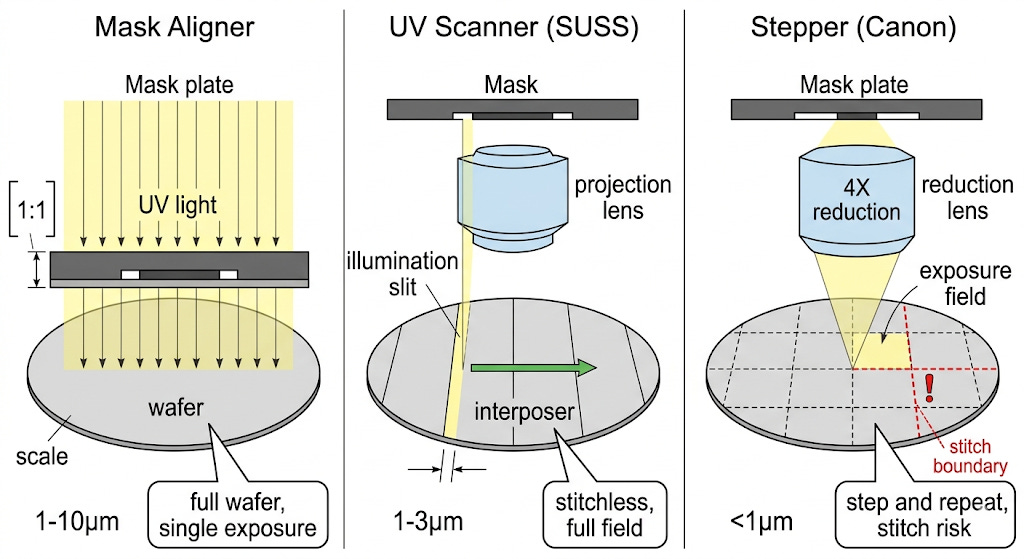

There are three different classes of tools that co-exist in the fab. Each prints a different feature size (kind of like DUV vs EUV).

Mask aligners (Suss) — the simplest tool. The mask sits in direct contact with or very close proximity to the wafer surface (contact/proximity exposure). No reduction optics — it’s a 1:1 projection. Light floods the whole wafer in one shot. Resolution is limited to roughly 1-10µm. Used for thick resist applications, MEMS structures, through-wafer vias, coarse metal layers, anything where you need deep focus into tall topography but don’t need fine resolution. Cheap to run, high throughput, works well on non-planar surfaces.

UV scanners (Suss) — one step up in resolution. Also 1X (no reduction), but uses projection optics and a continuous scanning motion to expose the full wafer in a single unstitched pass. Resolution roughly 1-3µm. The key use case is large-area backend structures — CoWoS interposers, RDL routing layers, fan-out packaging — where the die or package exceeds the reticle field of a stepper and stitching would kill yield. This is the specific niche SUSS owns.

Steppers (Canon dominates) — highest resolution backend tool. Uses reduction optics (2X or 4X) to project a smaller, highly detailed reticle onto a portion of the wafer, then steps and repeats across the surface. Gets down to sub-1µm resolution. Used for the finest RDL layers, fine bump patterning, anything requiring tight CD control. The tradeoff is stitching error at field boundaries and throughput penalty on large packages.

Suss has 60% share in mask aligners and a monopoly in UV scanners.

Mask aligners is a stagnant/mature market as processes become more advanced.

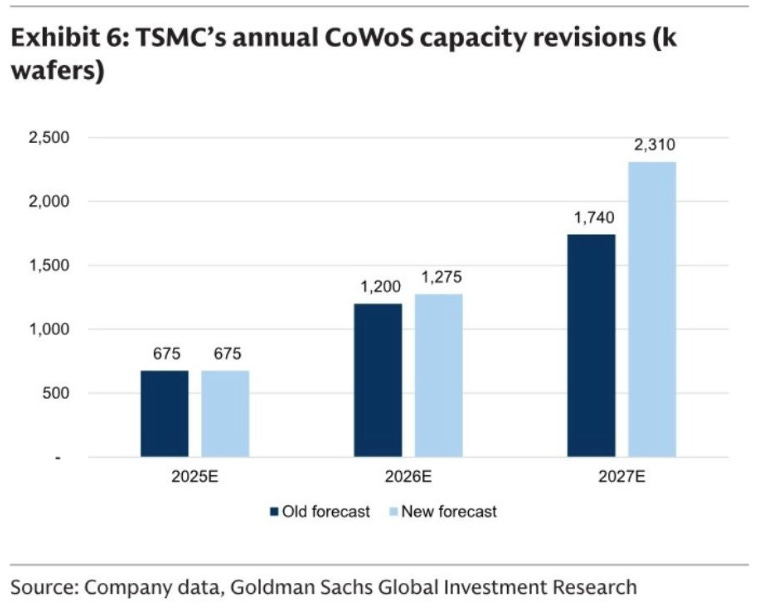

UV scanners is very important for CoWoS and they are sole source at TSMC. Once a tool is qualified into a process layer at TSMC, it doesn’t get swapped out. The integration is very deep. Process recipes, defect signatures, yield learning, PDK parameters all assume that specific tool’s optical characteristics.

In conclusion, UV scanners essentially scale with CoWoS expansion.

Front-End Photomask Solutions

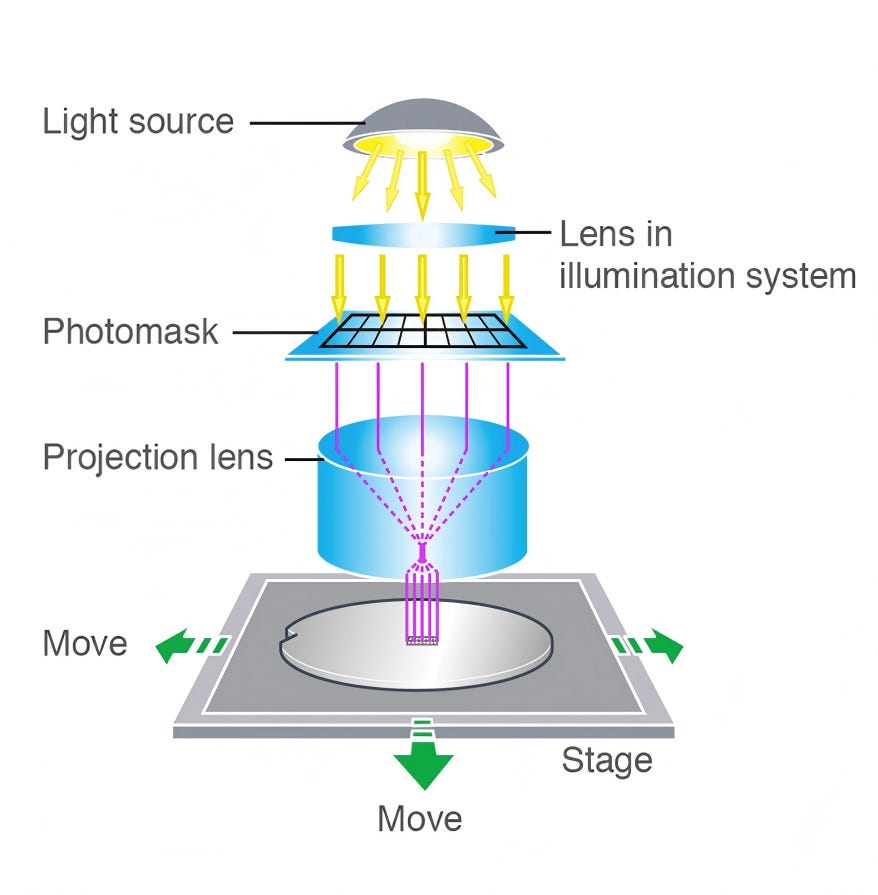

Photomasks are those stencils in the ASML lithography machine that the light shines through. A single particle on the mask will ruin every chip printed until someone realizes something is wrong. That’s why cleaning and processing the thing (what Suss does) is so important.

There are two separate processes Suss is involved in. First is cleaning, which is self-explanatory. Second is bake & develop. After a mask is exposed during its fabrication process, the bake step thermally hardens the exposed photoresist and the develop step washes away the unexposed portions, revealing the final absorber pattern that defines the circuit features on the mask.

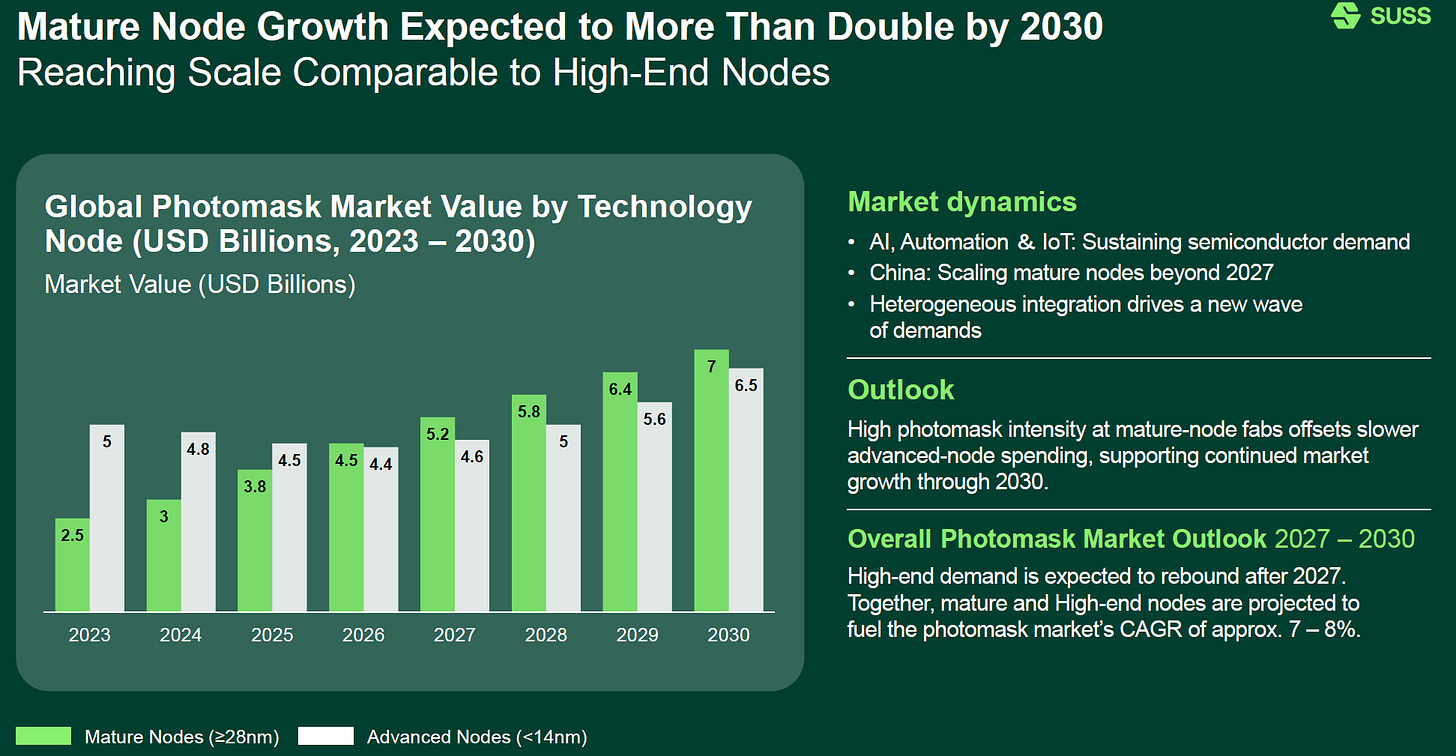

Seasoned semis investors probably notice something strange.

Mature nodes is growing faster than advanced nodes? That is really strange. That probably means they structurally undergrow EUV shipments or mature nodes are becoming more photomask intensive for whatever reason.

No. That’s probably not the case. This slide was from their capital markets day a year ago. Back then, N3 capacity was fine. ASML was in a deep drawdown. Memory makers were not begging ASML for EUV to do node transitions to resolve the DRAM crisis. In fact, DRAM wasn’t even in an upcycle yet! These numbers are so outdated they might as well be useless.

Photomask solutions should track EUV system shipments closely.

Mature nodes are 45% of the market while advanced nodes are 55%. Within advanced nodes they have a near monopoly on photomask cleaning. Within mature nodes they have only 15% share. Which means the VAST MAJORITY (80%+) of that 30% chunk of their revenue is directly correlated to ASML EUV shipments.

If you are bullish ASML, you have to be be bullish Suss.

Cyclical Trough

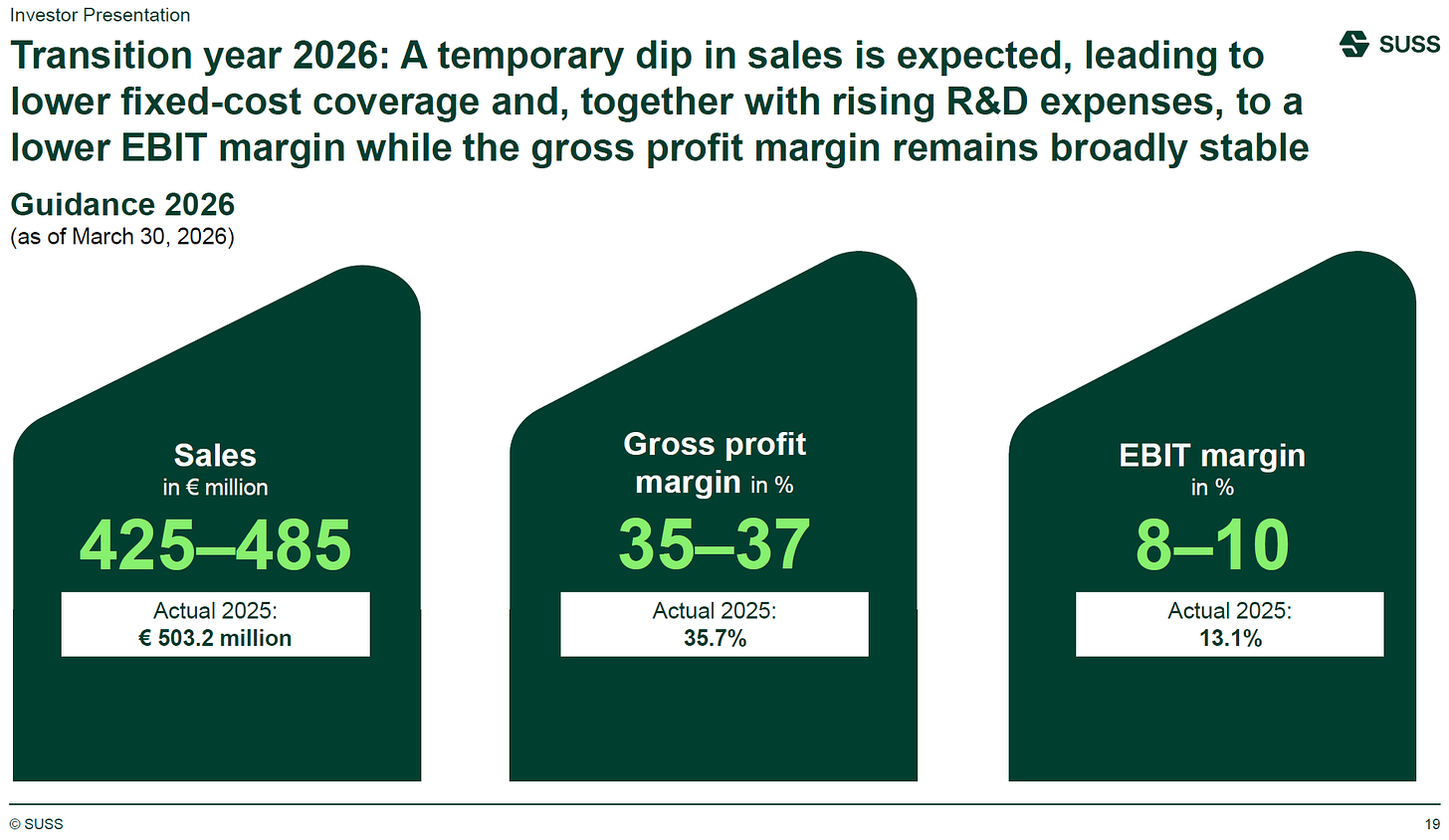

They will have a down year in 2026 that was widely anticipated by the sell-side and confirmed in earnings yesterday.

The reason is quite simple: As the HBM cartel transitions to HBM4, there is a pause in temporary bonder orders to re-tool in 2026.

This manifests as a low starting backlog / weak 2025 order trend problem, especially salient after a huge AI-driven 2024-25 surge results in bad comps. Mix is also worse in the trough as their bonders are relatively higher margin.

We should see this resolve no problem in 2027. This is in consensus and known by most market participants. It just looks scary at first glance so maybe keeps some marginal buyers out. There is nothing structurally wrong with the company.

Revenue Build, EPS Estimates, DCF Model

Below I share my projections for the 7 product lines in a detailed revenue build with segment-level shipment, ASP, and GM assumptions. Then, along with capex and aftermarket revenue projections, turn it into income statement EPS forecasts. And finally building a DCF.

I’ve also lowered my monthly subscription price by 30% so if you haven’t subscribed yet now is a great time to do so.